## 12. The TMS34010 Instruction Set

This section contains the TMS34010 instruction set (in alphabetical order). Related subjects, such as addressing modes, are presented first.

| Section |                                  | Page  |

|---------|----------------------------------|-------|

| 12.1    | Symbols and Abbreviations        |       |

| 12.2    | Addressing Modes                 | 12-3  |

|         | Move Instructions Summary        |       |

|         | PIXBLT Instructions Summary      |       |

| 12.5    | PIXT Instructions Summary        | 12-14 |

|         | TMS34010 Instruction Set Summary |       |

|         | Example Instruction              |       |

## 12.1 Symbols and Abbreviations

The symbols and abbreviations in Table 12-1 are used in the addressing modes discussion, the instruction set summary, and in the individual instruction descriptions.

Table 12-1. TMS34010 Instruction Set Symbol and Abbreviation Definitions

| Symbol          | Definition                                                                                                                                                                                                                                                                                                            | Symbol          | Definition                                                                                                                                                          |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Register File A | Registers A0-A14, including SP                                                                                                                                                                                                                                                                                        | Register File B | Registers B0-B14, including SP                                                                                                                                      |  |  |  |

| Rs              | Source register                                                                                                                                                                                                                                                                                                       | Rd              | Destination register                                                                                                                                                |  |  |  |

| RsX             | X half of source register                                                                                                                                                                                                                                                                                             | RsY             | Y half of source register                                                                                                                                           |  |  |  |

| RdX             | X half of destination register                                                                                                                                                                                                                                                                                        | Rd <b>Y</b>     | Y half of destination register                                                                                                                                      |  |  |  |

| An              | Register n in register file A                                                                                                                                                                                                                                                                                         | Bn              | Register n in register file B                                                                                                                                       |  |  |  |

| PC              | Program counter                                                                                                                                                                                                                                                                                                       | PC'             | PC prime. Specifies the PC of the next instruction (PC + instruction length)                                                                                        |  |  |  |

| ST              | Status register                                                                                                                                                                                                                                                                                                       | N               | Status sign bit                                                                                                                                                     |  |  |  |

| С               | Status carry bit                                                                                                                                                                                                                                                                                                      | z               | Status zero bit                                                                                                                                                     |  |  |  |

| V               | Status overflow bit                                                                                                                                                                                                                                                                                                   | IE              | Global interrupt enable bit                                                                                                                                         |  |  |  |

| SP              | Stack pointer                                                                                                                                                                                                                                                                                                         | TOS             | Top of stack                                                                                                                                                        |  |  |  |

| SAddress        | Source address                                                                                                                                                                                                                                                                                                        | DAddress        | Destination address                                                                                                                                                 |  |  |  |

| MSW             | Most significant word                                                                                                                                                                                                                                                                                                 | LSW             | Least significant word                                                                                                                                              |  |  |  |

| LSB             | Least significant bit                                                                                                                                                                                                                                                                                                 | MSB             | Most significant bit                                                                                                                                                |  |  |  |

| >               | Hexadecimal number                                                                                                                                                                                                                                                                                                    | к               | 5-bit constant                                                                                                                                                      |  |  |  |

| IW              | 16-bit immediate value                                                                                                                                                                                                                                                                                                | 1L              | 32-bit immediate value                                                                                                                                              |  |  |  |

| W               | 16-bit immediate value                                                                                                                                                                                                                                                                                                | L               | 32-bit immediate value                                                                                                                                              |  |  |  |

| F               | Field select. F=0 selects FS0, FE0<br>in the status register, F=1 selects<br>FS1, FE1                                                                                                                                                                                                                                 | R               | Register file select. Indicates<br>which register file (A or B) the<br>operand registers are in. R=0<br>specifies register file A, R=1<br>specifies register file B |  |  |  |

| ()              | In <b>Instruction syntax</b> , contents<br>of. For example, (Rd) specifies<br>the contents of the destination<br>register                                                                                                                                                                                             | :               | Concatenation. For example,<br>Rd:Rd + 1 means the concatena-<br>tion of one register and the next<br>into a 64-bit value, as in A0:A1                              |  |  |  |

| →               | Becomes the contents of                                                                                                                                                                                                                                                                                               | ~               | 1's complement                                                                                                                                                      |  |  |  |

|                 | Absolute value                                                                                                                                                                                                                                                                                                        | []              | Optional parameter                                                                                                                                                  |  |  |  |

| *               | Indirect addressing                                                                                                                                                                                                                                                                                                   | @               | Absolute addressing                                                                                                                                                 |  |  |  |

| <text></text>   | In <b>instruction syntax</b> , indicates a "fill in the blank" – substitute an actual value, address, or register for the text enclosed in the angle brackets. For example, substitute an actual source register for $\langle Rs \rangle$ ; substitute an actual destination address for $\langle DAddress \rangle$ . |                 |                                                                                                                                                                     |  |  |  |

## 12.2 Addressing Modes

The TMS34010 supports a variety of addressing modes. Most instructions use only one addressing mode; however, the MOVB, MOVE, and PIXT instructions each support several addressing modes. The following subsections describe the TMS34010 addressing modes.

### 12.2.1 Immediate Addressing

In this addressing mode, the source operand may be one of the following:

- A 16-bit immediate value (designated as IW)

- A 32-bit immediate value (designated as IL)

- A constant (designated as K)

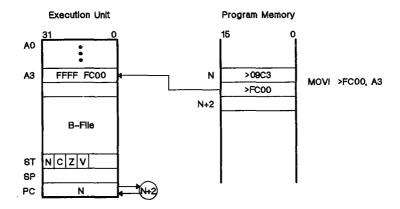

Figure 12-1 shows an example of the MOVI <IL>, <Rd> instruction. A 32-bit immediate value, >FC00, is loaded into the destination register, A3.

Figure 12-1. Immediate Addressing Mode

#### 12.2.2 Indirect XY

A source operand or a destination operand can be specified using this addressing mode.

- \**Rs.XY* The register contains the XY address of the data.

- \*Rd.XY The register contains the XY address where the data will be moved.

### 12.2.3 Absolute Addressing

A source operand or a destination operand can be specified as an absolute address.

- @SAddress The specified address contains the data.

- @DAddress The data will be moved into the specified address.

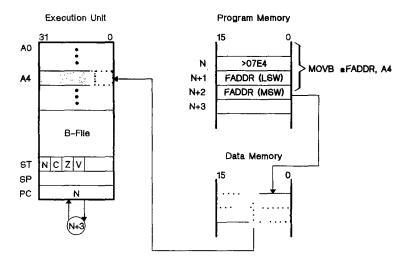

Figure 12-2 shows an example of the MOVB @<SAddress>, <Rd> instruction. In this example, the symbol *FADDR* represents a memory address; the data at this address are loaded into register A4.

Figure 12-2. Absolute Addressing Mode

#### 12.2.4 Register Direct

A source operand or a destination operand can be specified using register direct addressing mode.

- Rs The source register contains the data.

- Rd The data will be moved into the destination register.

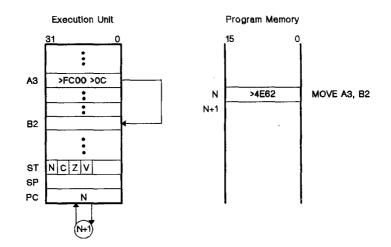

Figure 12-3 shows an example of the MOVE <Rs>,<Rd> instruction. The contents of the source register, A3, are moved into the destination register, B2.

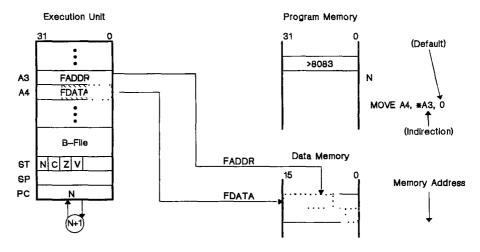

#### 12.2.5 Register Indirect

A source operand or a destination operand can be specified using register indirect addressing modé.

- \*Rs The register contains the address of the data.

- \*Rd The register contains the address where the data will be moved.

Figure 12-4 shows an example of the MOVE <Rs>, \*<Rd>, [<F>] instruction. Register A4 contains the source operand. Register A3 contains an address (represented by the symbol *FADDR*) where the data in A4 will be moved.

Figure 12-4. Register Indirect Addressing Mode

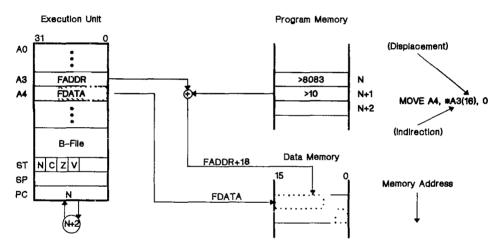

### 12.2.6 Register Indirect with Displacement

A source operand or a destination operand can be specified using this addressing mode.

- \*Rs(Displacement) The address of the data is found by adding the register contents to the signed displacement.

- \*Rd(Displacement) The data will be moved to the address specified by the sum register contents and the signed displacement.

Figure 12-5 shows an example of the MOVE  $\langle Rs \rangle$ ,  $\langle Rd \rangle$  ( $\langle Displacement \rangle$ ) instruction. Register A4 contains the source operand. Register A3 contains an address (represented by the symbol *FADDR*). The displacement, 16, is added to FADDR, to point to the location where the data in A4 will be moved. FS0 contains the field size.

Figure 12-5. Register Indirect with Displacement Addressing Mode

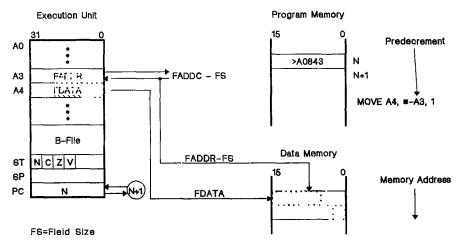

#### 12.2.7 Register Indirect with Predecrement

A source operand or a destination operand can be specified using this addressing mode.

- -\*Rs The address of the data is found by decrementing the register contents by the field size of the move.

- -\**Rd* The data will stored at the address found by decrementing the register contents by the field size of the move.

Figure 12-6 shows an example of the MOVE  $\langle Rs \rangle$ , \*- $\langle Rd \rangle$  instruction. Register A4 contains the source operand. Register A3 contains an address (represented by the symbol *FADDR*). This address is decremented by the field size of the move, so that it points to the location where the data in A4 will be moved. FS1 contains the field size.

Figure 12-6. Register Indirect with Predecrement Addressing Mode

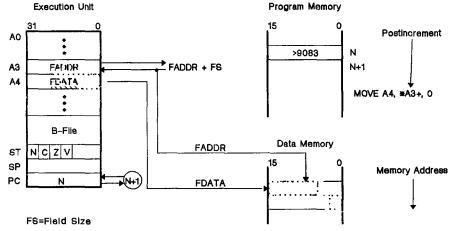

#### 12.2.8 Register Indirect with Postincrement

A source operand or a destination operand can be specified using this addressing mode.

- \**Rs*+ The register contains the address of the data. The register contents are incremented after the move.

- \**Rd*+ The register contains the address where the data will be moved. The register contents are incremented after the move.

Figure 12-7 shows an example of the MOVE <Rs>, \*-<Rd> instruction. Register A4 contains the source operand. Register A3 contains an address (represented by *FADDR*) where the data in A4 will be moved. The register contents are incremented after the move. FS0 contains the field size.

Figure 12-7. Register Indirect with Postincrement Addressing Mode

## 12.3 Move Instructions Summary

The move instructions use the GSP's bit-addressing and field operation capabilities to provide flexible memory management. All memory addresses for move operations are bit addresses. When a field is moved from memory to a register. Register bits to the left of the field are filled with either 0s or the sign bit, depending on the field extension mode. When a field is moved to memory from a register, the data for the field is assumed to be right justified within the register, and the bits to the left of the field are ignored. Table 12-2 summarizes the GSP move instructions.

| Move Type         | Mnemonic | Description                                              |

|-------------------|----------|----------------------------------------------------------|

| Register          | MOVE     | Move register to register                                |

| Constant          | ΜΟΥΚ     | Move constant (5 bits)                                   |

|                   | MOVI     | Move immediate (16 bits)                                 |

|                   | MOVI     | Move immediate (32 bits)                                 |

| XY                | MOVX     | Move 16 LSBs of register (X half)                        |

|                   | MOVY     | Move 16 MSBs of register (Y half)                        |

| Multiple Register | MMFM     | Move multiple registers from memory                      |

|                   | MMTM     | Move multiple registers to memory                        |

| Byte              | MOVB     | Move byte (8 bits, 9 addressing modes)                   |

| Field             | MOVE     | Move field to/from memory/register (15 addressing modes) |

Table 12-2. Summary of Move Instructions

#### 12.3.1 Register-to-Register Moves

The register-to-register MOVE instruction moves data directly between register files A and B. This is a 32-bit move; the entire contents of the destination register are replaced.

#### 12.3.2 Constant-to-Register Moves

The MOVK and MOVI instructions load a register with a constant value. MOVK places a zero-extended value of 1 to 32 in the register. MOVI has two modes, 16-bit and 32-bit. The 32-bit MOVI uses two extension words which explicitly define the value to be stored in the register. The extension word for the 16-bit MOVI contains a value which is sign extended to 32 bits when moved into the register. Use the CLR instruction to store 0 in a register.

#### 12.3.3 X and Y Register Moves

The MOVX and MOVY instructions move the X and Y halves, respectively; the other half of the destination register is not affected. These are 16-bit moves within the register file. XY addressing is discussed in Section 4.

#### 12.3.4 Multiple Register Moves

Multiple-register moves save and restore select members of up to an entire file of registers to memory. A 16-bit mask specifies which of the 16 registers in the designated file are to be moved to or from memory. One register from the selected file acts as a pointer register for the move. Any of the registers in the file, including the SP, may be used as the pointer register. The selected registers are input as a list; the assembler checks that they and the pointer register are all in the same file. The pointer register contains a bit address for the register "stack." The stacking operation follows the same conventions as the system stack, growing in the direction of lower memory. If the SP is used, both register files may be moved to the same stack area (since SP may be accessed from both files). MMTM moves multiple registers to the stack while MMFM moves them from memory back to the register file.

#### 12.3.5 Byte Moves

Byte moves are special 8-bit cases of the field moves described in Section 12.3.6. Byte moves are implicitly 8-bit moves. They transfer data:

- From memory to a register (using field extraction),

- From a register to memory (using field insertion), or

- From memory to memory (using field extraction and field insertion).

A byte can begin on any bit boundary within a word. When a byte is moved from memory to a general-purpose register, it is right justified within the register so that the LSB of the byte coincides with the rightmost bit (bit 0) of the register. The byte is sign extended to fill the 24 MSBs of the register.

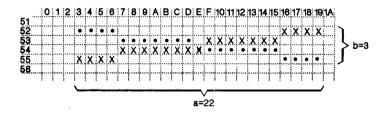

Table 12-3 lists the possible combinations of source and destination addressing modes for MOVBs.

| Source             | Destination Addressing Mode |     |           |          |  |  |  |

|--------------------|-----------------------------|-----|-----------|----------|--|--|--|

| Addressing<br>Mode | Rd                          | *Rd | *Rd(disp) | @Address |  |  |  |

| Rs                 |                             | •   | •         | •        |  |  |  |

| *Rs                | •                           | •   |           |          |  |  |  |

| *Rs(Disp)          | •                           |     | •         |          |  |  |  |

| @Address           | •                           |     |           | •        |  |  |  |

Table 12-3. MOVB Addressing Modes

Note: The ● symbol indicates a valid operation; a blank box indicates an invalid operation.

Sequences of byte-move operations can be expected to execute more efficiently if the byte address points to an even 8-bit boundary within memory. This occurs when the three LSBs of the 32-bit starting address of the byte are 0. A byte that straddles a word boundary requires twice as many memory cycles to access.

### 12.3.6 Field Moves

A field is a configurable data structure in memory. It is identified by two parameters – size and data address. A field's length can be defined to be any value from 1 to 32 bits. Field moves manipulate arbitrarily-sized data fields in memory and the register file.

- Field data in *memory* is addressed by its bit address and is treated as a string of contiguous bits; it may start at any bit address in memory.

- Field data in *the register file* is right justified in the register; the LSB of the field is stored in the LSB of the register.

When field data is moved into a register, it is right justified within the register. The register bits to the left of the field are all 1s or all 0s, depending on the values of both the appropriate FE (field extension) bit in the status register, and sign bit (MSB) of the field. If FE=1, the field is sign extended; if FE=0, the field is zero extended. When data is moved from a register, these non-field bits of the register are ignored.

Fields are transferred between the general-purpose registers and memory by means of the memory-to-register and register-to-memory move instructions. Fields are transferred from one memory location to another via the memory-to-memory move instructions.

Table 12-4 lists the possible combinations of source and destination addressing modes for MOVEs.

| Source<br>Addressing | Destination Addressing Mode |     |      |      |           |          |  |  |  |

|----------------------|-----------------------------|-----|------|------|-----------|----------|--|--|--|

| Mode                 | Rd                          | *Rd | *Rd+ | -*Rd | *Rd(disp) | @Address |  |  |  |

| Rs                   |                             |     | •    | •    | •         | •        |  |  |  |

| *Rs                  | •                           | •   |      |      |           |          |  |  |  |

| *Rs+                 | •                           |     | •    |      |           |          |  |  |  |

| -*Rs                 | •                           |     |      | •    |           |          |  |  |  |

| *Rs(Disp)            | •                           |     | •    |      | •         |          |  |  |  |

| @Addr                | •                           |     | •    |      |           | •        |  |  |  |

Table 12-4. Field Move Addressing Modes

Note: The • symbol indicates a valid operation; a blank box indicates an invalid operation.

Two field sizes are simultaneously available for field moves. The lengths of fields 0 and 1 are defined by two 5-bit fields in the status register, FS0 and FS1. The status register also contains the FE0 and FE1 parameters, which define the field extension properties of the data when it is moved into a register.

The SETF instruction specifies the size and signed/unsigned condition of either field 0 or 1 by placing this data in one of two 6-bit fields located in the

status register. One bit specifies sign/zero extension, and five bits store the field size (in bits).

The EXGF instruction may also set either of the two field types, while preserving a copy of the previous definition.

The address of a field points to its least significant bit. A field can begin at an arbitrary bit address in memory. Field data addresses for particular moves are derived from values in registers and extension words following the instruction. Field moves transfer data:

- From memory to a register (using field extraction),

- From a register to memory (using field insertion), or

- From memory to memory (using field extraction and field insertion).

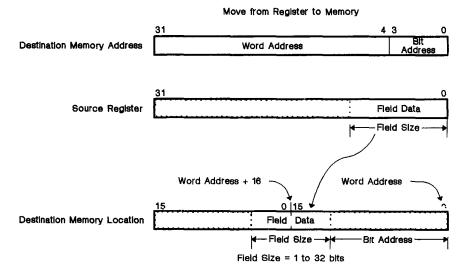

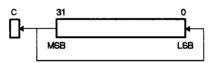

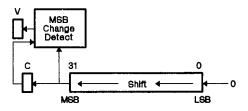

#### 12.3.6.1 Register-to-Memory Field Moves

Figure 12-8 illustrates the register-to-memory move operation. In this type of move, the source register contains the right-justified field data (width is specified by the field size). The destination memory location is the bit position pointed to by the destination memory address. The address consists of a portion defining the starting word in which the field is to be written and an offset into that word, the bit address. Depending on the bit address within this word and the field size, the destination location may extend into two or more words. The field size for the move is one of two indirect values stored in ST, as selected by the programmer. The field extension bit is not used.

Figure 12-8. Register-to-Memory Moves

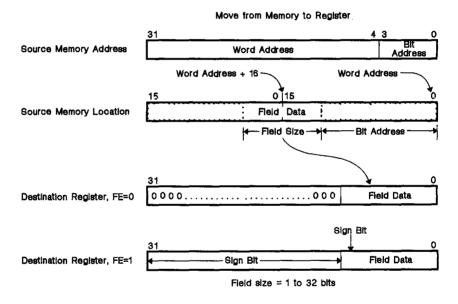

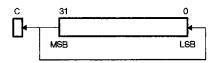

#### 12.3.6.2 Memory-to-Register Field Moves

Figure 12-9 shows the memory-to-register move operation. The source memory location is the bit position pointed to by the source memory address. The address consists of a portion defining the starting word in which the field is to be written and an offset into that word, the bit address. Depending on the bit address within this word and the field size, the source location may extend into two or more words. After the move, the destination register LSBs contain the right-justified field data (width is specified by the field size). The MSBs of the register contain either all 1s or all 0s. If the sign extension bit FE0 or FE1 associated with the field size selected is 0, the MSBs are 0s. If the sign extension bit selected is 1, the MSBs contain the value of the sign bit of the field data (its MSB). The field size for the move is one of two indirect values stored in ST, as selected by the programmer.

Figure 12-9. Memory-to-Register Moves

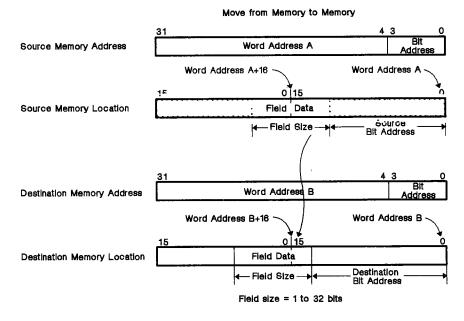

#### 12.3.6.3 Memory-to-Memory Field Moves

Figure 12-10 shows a memory-to-memory field move operation. The source memory location is the bit position pointed to by the source memory address. The destination memory location is the bit position pointed to by the destination memory address. Depending on the bit addresses within the respective words and the field size, either the source location or destination locations may extend into two or more words. After the move, the destination location contains the field data from the source memory location. The field size for the move is one of two indirect values stored in ST, as selected by the programmer. The field extension bit is not used.

Figure 12-10. Memory-to-Memory Moves

## 12.4 PIXBLT Instructions Summary

The TMS34010 supports 6 different PIXBLT instructions. PIXBLTs vary according to the format of the source and destination pixel blocks. Table 12-5 summarizes the PIXBLT instructions.

| Syntax       | Formats          | Page   |

|--------------|------------------|--------|

| PIXBLT B,L   | Binary to linear | 12-157 |

| PIXBLT B,XY  | Binary to XY     | 12-162 |

| PIXBLT L,L   | Linear to linear | 12-169 |

| PIXBLT L,XY  | Linear to XY     | 12-175 |

| PIXBLT XY,L  | XY to linear     | 12-181 |

| PIXBLT XY,XY | XY to XY         | 12-186 |

Table 12-5. PIXBLT Instruction Summary

## 12.5 PIXT Instructions Summary

The PIXT instructions move single pixels. The pixel may originate from a register or a memory location, and may be moved to a register or a memory location. There are 6 variations of the PIXT instruction; each uses a different combination of the addressing modes described in Section 12.2.

Table 12-6 lists the possible combinations of source and destination addressing modes for PIXTs.

| Source             | Destina | tion Addressi | ing Mode |

|--------------------|---------|---------------|----------|

| Addressing<br>Mode | Rd      | *Rd           | *Rd.XY   |

| Rs                 |         | •             | •        |

| *Rs                | ٠       | •             |          |

| *Rs.XY             |         | •             | •        |

Table 12-6. PIXT Addressing Modes

Note: The ● symbol indicates a valid operation; a blank box indicates an invalid operation.

| Graphics Instructions                                            |       |                   |      |          |        |      |

|------------------------------------------------------------------|-------|-------------------|------|----------|--------|------|

| Syntax and Description                                           | Words | Machine<br>States | MSB  | 16-Bit ( | Opcode | LSB  |

| ADDXY Rs,Rd<br>Add registers in XY mode                          | 1     | 1,4               | 1110 | 0005     | SSSR   | DDDD |

| CMPXY Rd,Rd<br>Compare X and Y halves of registers               | 1     | 3,6               | 1110 | 0105     | SSSR   | DDDD |

| CPW Rs,Rd<br>Compare point to window                             | 1     | 1,4               | 1110 | 0115     | SSSR   | DDDD |

| CVXYL Rs,Rd<br>Convert XY address to linear address              | 1     | 3,6               | 1110 | 1005     | SSSR   | DDDD |

| DRAV Rs,Rd<br>Draw and advance                                   | 1     | t                 | 1111 | 0115     | SSSR   | DDDD |

| FILL L<br>Fill array with processed pixels, linear               | 1     | ±                 | 0000 | 1111     | 1100   | 0000 |

| FILL XY<br>Fill array with processed pixels, XY                  | 1     | ‡                 | 0000 | 1111     | 1110   | 0000 |

| MOVX Rs,Rd<br>Move X half of register                            | 1     | 1,4               | 1110 | 1105     | SSSR   | DDDD |

| MOVY Rs,Rd<br>Move Y half of register                            | 1     | 1,4               | 1110 | 1115     | SSSR   | DDDD |

| PIXBLT B,L<br>Pixel block transfer, binary to linear             | 1     | ‡‡                | 0000 | 1111     | 1000   | 0000 |

| PIXBLT B,XY<br>Pixel block transfer and expand, binary to XY     | 1     | ‡‡                | 0000 | 1111     | 1010   | 0000 |

| PIXBLT L,L<br>Pixel block transfer, linear to linear             | 1     | ş                 | 0000 | 1111     | 0000   | 0000 |

| PIXBLT L,XY<br>Pixel block transfer, linear to XY                | 1     | 5                 | 0000 | 1111     | 0010   | 0000 |

| PIXBLT XY,L<br>Pixel block transfer, XY to linear                | 1     | ş                 | 0000 | 1111     | 0100   | 0000 |

| PIXBLT XY,XY<br>Pixel block transfer, XY to XY                   | 1     | ş                 | 0000 | 1111     | 0110   | 0000 |

| PIXT Rs,*Rd<br>Pixel transfer, register to indirect              | 1     | †                 | 1111 | 1005     | SSSR   | DDDD |

| PIXT Rs,*Rd.XY<br>Pixel transfer, register to indirect XY        | 1     | +                 | 1111 | 0005     | SSSR   | DDDD |

| PIXT *Rs,Rd<br>Pixel transfer, indirect to register              | 1     | t                 | 1111 | 101S     | SSSR   | DDDD |

| PIXT *Rs,*Rd<br>Pixel transfer, indirect to indirect             | 1     | †                 | 1111 | 1105     | SSSR   | DDDD |

| PIXT *Rs.XY,Rd<br>Pixel transfer, indirect XY to register        | 1     | †                 | 1111 | 0015     | SSSR   | DDDD |

| PIXT *Rs.XY,*Rd.XY<br>Pixel transfer, indirect XY to indirect XY | 1     | t                 | 1111 | 0105     | SSSR   | DDDD |

| SUBXY Rs,Rd<br>Subtract registers in XY mode                     | 1     | 1,4               | 1110 | 001S     | SSSR   | DDDD |

| LINE Z<br>Line draw                                              | 1     | Δ                 | 1101 | 1111     | Z001   | 1010 |

#### Table 12-7. TMS34010 Instruction Set Summary

See instruction

See Section 13.3, FILL Instructions Timing

See Section 13.5, PIXBLT Expand Instructions Timing

See Section 13.4, PIXBLT Instructions Timing

Δ See Section 13.6, The LINE Instruction Timing

| Move In                                                                                            | struction | าร                |      |        |        |      |

|----------------------------------------------------------------------------------------------------|-----------|-------------------|------|--------|--------|------|

| Syntax and Description                                                                             | Words     | Machine<br>States | MSB  | 16-Bit | Opcode | LSB  |

| MOVB Rs,*Rd<br>Move byte, register to indirect                                                     | 1         | ٩ï                | 1000 | 1105   | SSSR   | DDDD |

| MOVB *Rs,Rd<br>Move byte, indirect to register                                                     | 1         | ۹                 | 1000 | 1115   | SSSR   | DDDD |

| MOVB *Rs,*Rd<br>Move byte, indirect to indirect                                                    | 1         | ٩                 | 1001 | 1105   | SSSR   | DDDD |

| MOVB *Rs,*Rd(Disp)<br>Move byte, register to indirect with displacement                            | 2         | १                 | 1010 | 1105   | SSSR   | DDDD |

| MOVB *Rs(Disp),Rd<br>Move byte, indirect with displacement to register                             | 2         | f                 | 1010 | 1115   | SSSR   | DDDD |

| MOVB *Rs(Disp),*Rd(Disp)<br>Move byte, indirect with displacement to indirect<br>with displacement | 3         | १                 | 1011 | 1105   | SSSR   | DDDD |

| MOVB Rs,@DAddress<br>Move byte, register to absolute                                               | 3         | ¶                 | 0000 | 0101   | 111R   | SSSS |

| MOVB @SAddress,Rd<br>Move byte, absolute to register                                               | 3         | f                 | 0000 | 0111   | 111R   | DDDD |

| MOVB @SAddress,@DAddress<br>Move byte, absolute to absolute                                        | 5         | ۹                 | 0000 | 0011   | 0100   | 0000 |

| MOVE Rs,Rd<br>Move register to register                                                            | 1         | 1,4               | 0100 | 1 1MS  | SSSR   | DDDD |

| MOVE Rs,*Rd,F<br>Move field, register to indirect                                                  | 1         | শ                 | 1000 | 00FS   | SSSR   | DDDD |

| MOVE Rs,-*Rd,F<br>Move field, register to indirect (predecrement)                                  | 1         | १                 | 1010 | 00FS   | SSSR   | DDDD |

| MOVE Rs,*Rd+,F<br>Move field, register to indirect (postincrement)                                 | 1         | १                 | 1001 | 00FS   | SSSR   | DDDD |

| MOVE *Rs,Rd,F<br>Move field, indirect to register                                                  | 1         | শ                 | 1000 | 01 F S | SSSR   | DDDD |

| MOVE -*Rs,Rd,F<br>Move field, indirect (predecrement) to register                                  | 1         | শ                 | 1010 | 01 F S | SSSR   | DDDD |

| MOVE *Rs+,Rd,F<br>Move field, indirect (postincrement) to register                                 | 1         | ¶T                | 1001 | 01 F S | SSSR   | DDDD |

| MOVE *Rs,*Rd,F<br>Move field, indirect to indirect                                                 | 1         | ¶T                | 1000 | 10FS   | SSSR   | DDDD |

| MOVE -*Rs,-*Fd,F<br>Move field, indirect (predecrement) to indirect<br>(predecrement)              | 1         | ¶                 | 1010 | 10FS   | SSSR   | DDDD |

| MOVE *Rs+,*Rd+,F<br>Move field, indirect (postincrement) to indirect<br>(postincrement)            | 1         | n                 | 1001 | 10FS   | SSSR   | DDDD |

| MOVE Rs,*Rd(Disp),F<br>Move field, register to indirect with displacement                          | 2         | ¶                 | 1011 | 00FS   | SSSR   | DDDD |

| MOVE *Rs(Disp),Rd,F<br>Move field, indirect with displacement to register                          | 2         | ¶                 | 1011 | 01FS   | SSSR   | DDDD |

## Table 12-7. TMS34010 Instruction Set Summary (Continued)

1 See Section 13.2, MOVE and MOVB Instructions Timing

| Move Instruct                                                                                         | ions (Cor | ntinued)          |      |        | ······ |          |

|-------------------------------------------------------------------------------------------------------|-----------|-------------------|------|--------|--------|----------|

| Syntax and Description                                                                                | Words     | Machine<br>States | мѕв  | 16-Bit | Opcode | LSB      |

| MOVE *Rs(Disp),*Rd+,F<br>Move field, indirect with displacement to indirect<br>(postincrement)        | 2         | π                 | 1101 | 00FS   | SSSR   | DDDD     |

| MOVE *Rs(Disp),*Rd(Disp),F<br>Move field, indirect with displacement to indirect<br>with displacement | 3         | ¶                 | 1011 | 10FS   | SSSR   | DDDD     |

| MOVE Rs,@DAddress,F<br>Move field, register to absolute                                               | 3         | П                 | 0000 | 01 F 1 | 100R   | DDDD     |

| MOVE @SAddress,Rd,F<br>Move field, absolute to register                                               | 3         | ी                 | 0000 | 01 F 1 | 101 R  | DDDD     |

| MOVE @SAddress,*Rd+,F<br>Move field, absolute to indirect (postincrement)                             | 3         | গ                 | 1101 | 01F0   | 000R   | DDDD     |

| MOVE @SAddress,@DAddress,F<br>Move field, absolute to absolute                                        | 5         | Π                 | 0000 | 01F1   | 1100   | DDDD     |

| General                                                                                               | nstructio | ons               | L.,  |        |        |          |

| Syntax and Description                                                                                | Words     | Machine<br>States | мѕв  | 16-Bit | Opcode | ,<br>LSB |

| ABS Rd<br>Store absolute value                                                                        | 1         | 1,4               | 0000 | 0011   | 100R   | DDDD     |

| ADD Rs,Rd<br>Add registers                                                                            | 1         | 1,4               | 0100 | 0005   | SSSR   | DDDD     |

| ADDC Rs,Rd<br>Add registers with carry                                                                | 1         | 1,4               | 0100 | 001S   | SSSR   | DDDD     |

| ADDI IW,Rd<br>Add immediate (16 bits)                                                                 | 2         | 2,8               | 0000 | 1011   | 000R   | DDDD     |

| ADDI IL.Rd<br>Add immediate (32 bits)                                                                 | 3         | 3,12              | 0000 | 1011   | 001 R  | DDDD     |

| ADDK K,Rd<br>Add constant (5 bits)                                                                    | 1         | 1,4               | 0001 | 00KK   | KKKR   | DDDD     |

| AND Rs,Rd<br>AND registers                                                                            | 1         | 1,4               | 0101 | 0005   | SSSR   | DDDD     |

| ANDI IL,Rd<br>AND immediate (32 bits)                                                                 | 3         | 3,12              | 0000 | 1011   | 100R   | DDDD     |

| ANDN Rs,Rd<br>AND register with complement                                                            | 1         | 1,4               | 0101 | 001 S  | SSSR   | DDD      |

| ANDNI IL,Rd<br>AND not immediate (32 bits)                                                            | 3         | 3,12              | 0000 | 1011   | 100R   | DDDD     |

| BTST K,Rd<br>Test register bit, constant                                                              | 1         | 1,4               | 0001 | 11KK   | KKKR   | DDDD     |

| BTST Rs,Rd<br>Test register bit, register                                                             | 1         | 2,5               | 0100 | 1015   | SSSR   | DDDD     |

| CLR Rd<br>Clear register                                                                              | 1         | 1,4               | 0101 | 011 D  | DDDR   | DDDD     |

| CLRC<br>Clear carry                                                                                   | 1         | 1,4               | 0000 | 0011   | 0010   | 0000     |

| CMP Rs,Rd<br>Compare registers                                                                        | 1         | 1,4               | 0000 | 1011   | 01 0 R | DDDD     |

## Table 12-7. TMS34010 Instruction Set Summary (Continued)

T See Section 13.2, MOVE and MOVB Instructions Timing

| General Instructions (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                             |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Words                            | Machine<br>States                                                                                                                                                                                                                                                                                                                                                                                                           | MSB                                                                                                                                         | 16-Bit                                                                                                                                                                                                                             | Opcode                                                                                                                                                                                                                                                                                                      | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                                | 2,8                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000                                                                                                                                        | 1011                                                                                                                                                                                                                               | 010R                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3                                | 3,12                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000                                                                                                                                        | 1011                                                                                                                                                                                                                               | 011R                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 1,4                                                                                                                                                                                                                                                                                                                                                                                                                         | 0001                                                                                                                                        | 0100                                                                                                                                                                                                                               | 001 R                                                                                                                                                                                                                                                                                                       | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 3,6                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000                                                                                                                                        | 0011                                                                                                                                                                                                                               | 0110                                                                                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 40,43<br>39,42 Δ                                                                                                                                                                                                                                                                                                                                                                                                            | 0101                                                                                                                                        | 1005                                                                                                                                                                                                                               | SSSR                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 37,40                                                                                                                                                                                                                                                                                                                                                                                                                       | 0101                                                                                                                                        | 101S                                                                                                                                                                                                                               | SSSR                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 3,6                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000                                                                                                                                        | 1101                                                                                                                                                                                                                               | 0110                                                                                                                                                                                                                                                                                                        | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 1,4                                                                                                                                                                                                                                                                                                                                                                                                                         | 1101                                                                                                                                        | 01 F 1                                                                                                                                                                                                                             | 000R                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 1,4                                                                                                                                                                                                                                                                                                                                                                                                                         | 0110                                                                                                                                        | 101S                                                                                                                                                                                                                               | SSSR                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2                                | †                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000                                                                                                                                        | 1001                                                                                                                                                                                                                               | 101 R                                                                                                                                                                                                                                                                                                       | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2                                | +                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000                                                                                                                                        | 1001                                                                                                                                                                                                                               | 100R                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 40,43                                                                                                                                                                                                                                                                                                                                                                                                                       | 0110                                                                                                                                        | 1105                                                                                                                                                                                                                               | SSSR                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                | 35,38                                                                                                                                                                                                                                                                                                                                                                                                                       | 0110                                                                                                                                        | 111S                                                                                                                                                                                                                               | SSSR                                                                                                                                                                                                                                                                                                        | DDDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |