Whitepaper

# **NVIDIA GeForce GTX 980**

Featuring Maxwell, The Most Advanced GPU Ever Made.

V1.1

# **Table of Contents**

| Introduction                                                              |

|---------------------------------------------------------------------------|

| Extraordinary Gaming Performance for the Latest Displays                  |

| Incredible Energy Efficiency4                                             |

| Dramatic Leap Forward In Lighting with VXGI5                              |

| GM204 Hardware Architecture In-Depth6                                     |

| Maxwell Streaming Multiprocessor8                                         |

| PolyMorph Engine 3.09                                                     |

| GM204 Memory Subsystem10                                                  |

| New Display and Video Engines                                             |

| Maxwell: Enabling The Next Frontier in PC Graphics13                      |

| Hardware Acceleration for VXGI – Multi-Projection and Conservative Raster |

| Tiled Resources                                                           |

| Raster Ordered View24                                                     |

| DirectX 1225                                                              |

| Advancing the State-Of-The-Art in Image Quality27                         |

| Dynamic Super Resolution                                                  |

| Conclusion                                                                |

| LEGAL NOTICE                                                              |

# Introduction

In our 21-year quest to bring the most realistic 3D graphics to gamers, NVIDIA has introduced a number of innovations. With its hardware transform and lighting engine, NVIDIA's GeForce 256 ushered in the era of the GPU in 1999, bringing T&L support to consumer graphics for the first time. In late 2006 with the G80 GPU and the GeForce 8800 GTX graphics board, CUDA and the formalization of GPGPU computing as we know it today was first brought to the world. More recently, in 2010 we launched the GeForce GTX 480—our first GPU built using the Fermi graphics architecture. GeForce GTX 480 incorporated fifteen parallel tessellation units, enabling dramatic speedups in geometry processing compared to prior GPUs. With great strides in architectural efficiency, Kepler GPUs delivered significantly improved performance and power efficiency when introduced in 2012.

Earlier this year we launched the GeForce GTX 750 Ti, our first GPU from the Maxwell architectural family. Maxwell GPUs were designed from the ground up for extreme power efficiency and exceptional performance per watt consumed. In many DX11 applications, the GTX 750 Ti is capable of matching or even beating the performance of our once flagship GeForce GTX 480, while consuming only a fourth the power. Thanks to its remarkable power efficiency, our first generation Maxwell GPUs were ideal for use in power-limited environments like notebooks and small form factor PCs, in addition to mainstream desktops.

NVIDIA's latest GPU, GM204, is the first to use the full realization of our 10<sup>th</sup> generation GPU architecture, Maxwell. Our design goals for GM204 were to deliver:

- Extraordinary Gaming Performance for the Latest Displays

- Incredible Energy Efficiency

- Dramatic Leap Forward In Lighting With VXGI

### **Extraordinary Gaming Performance for the Latest Displays**

After years of little or no progress in the evolution of PC displays, the pace of new technology introductions has dramatically increased. Screen resolutions are growing, with the first 4K displays for gamers hitting the market a little over a year ago. While 4K was initially expensive, thanks to rapidly falling prices, 4K adoption is now beginning to take off. In order to drive all these pixels, GM2xx GPUs were designed to deliver more performance at the highest resolutions, and also support new display tech for 4K like HDMI 2.0. In addition, with Dynamic Super Resolution, Maxwell introduces the ability to significantly enhance display quality on sub-4K displays by rendering at higher resolution and then applying an advanced resizing filter that leverages the high resolution information.

Virtual Reality displays are another area that is likely to drive a dramatic increase in rendering rate requirements. Two displays for two eyes doubles the rendering workload, and ever higher resolution and refresh rate capability will be crucial to eliminating rendering artifacts that break the illusion of reality for the VR user.

### **Incredible Energy Efficiency**

All GeForce GPUs are made to deliver performance leadership in their respective segment. But PC gamers also expect efficiency—not noisy fans, excessive heat, and over-taxed power supplies. The desktop PC gaming market is seeing increasing popularity of smaller and thinner form factors, and the laptop PC gaming market has grown explosively in the past few years.

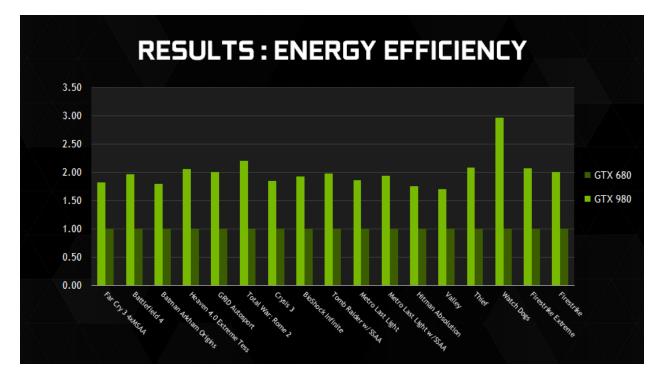

The Maxwell architecture was designed to provide an extraordinary leap in power efficiency and deliver unrivaled performance while simultaneously reducing power consumption from the previous generation. With a combination of advances originally developed for Tegra K1, new architectural approaches seen first in the GeForce GTX 750 Ti, and further refinement for GM204, Maxwell now delivers 2x the performance per watt compared to Kepler products.

Figure 1: GM204 delivers 2X higher perf/watt compared to Kepler

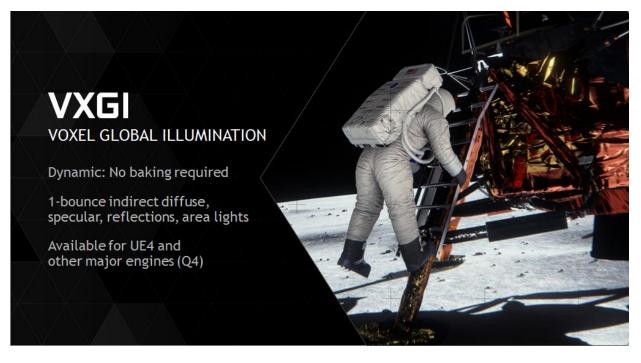

# Dramatic Leap Forward In Lighting with VXGI

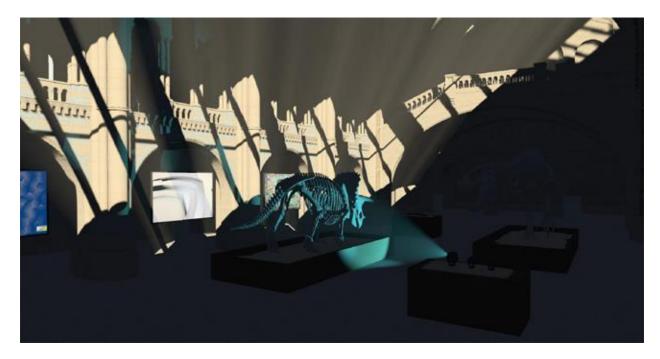

Lighting is the biggest hurdle in computer graphics that must be overcome in order to achieve photorealism. Global illumination gets us significantly closer to achieving this goal. Global illumination is often used in the movie industry to produce CG scenes that look stunning, but rendering truly dynamic global illumination in real time on the GPU has been impractical until now.

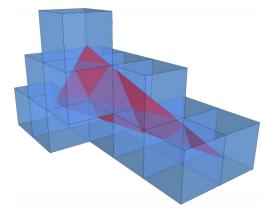

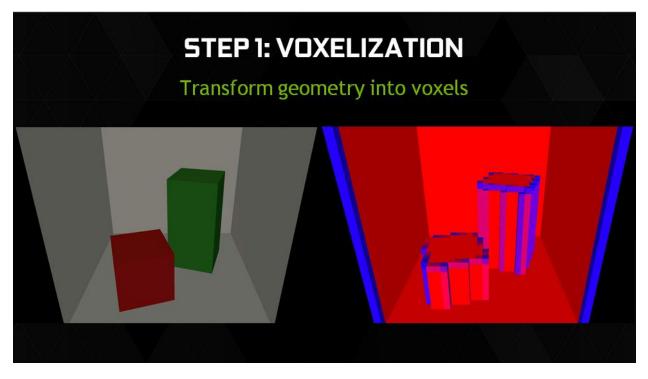

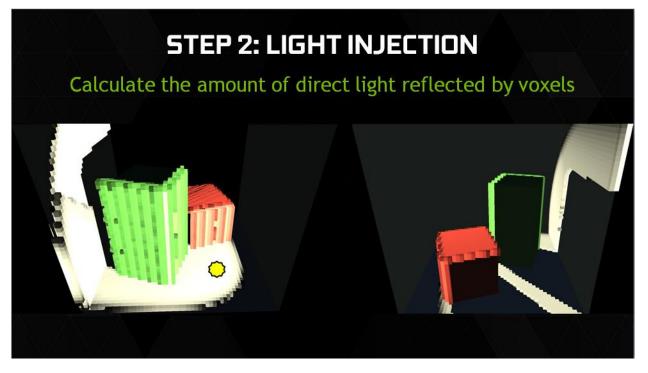

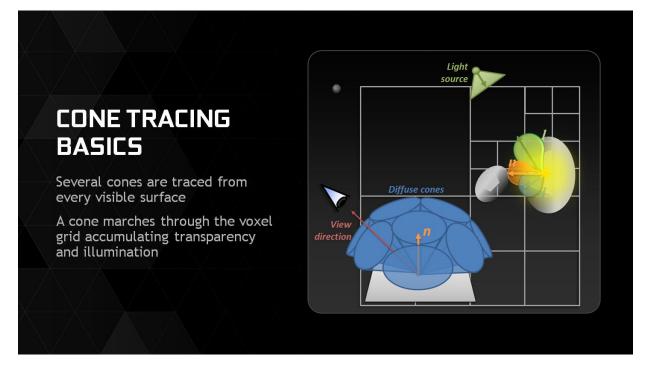

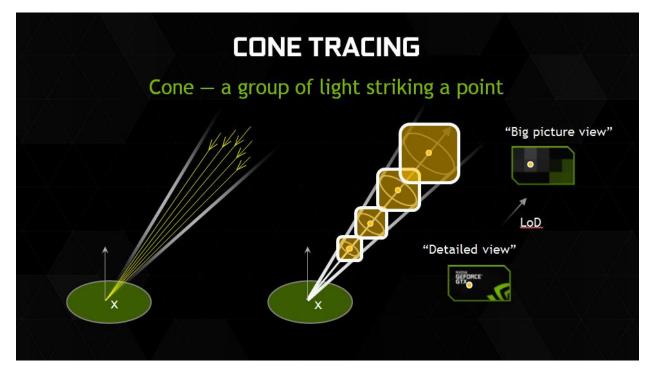

NVIDIA Voxel Global Illumination (VXGI) is the next big leap forward in lighting. VXGI is based on the concept pioneered by NVIDIA researcher Cyril Crassin in 2011, of using a 3D data structure ("voxels") to capture coverage and lighting information at every point in the scene. This data structure can then be traced during the final rendering stage to accurately determine the effect of light bouncing around in the scene.

Cyril's original implementation relied on voxels that were stored in an octree structure. While it was able to run successfully on a GeForce GTX 680, it had limitations. We've spent the last three years developing an implementation that can be accelerated natively by the GPU, as well as improving the algorithm. The result of that effort is VXGI.

VXGI provides dramatically improved performance for global illumination. While VXGI's software algorithm will run on all GPUs, the performance benefits of VXGI hardware acceleration will only be available on our latest Maxwell GPUs.

The first graphics cards to ship with our new GM204 GPU are the GeForce GTX 980 and GeForce GTX 970. For simplicity purposes we'll be focusing solely on the GeForce GTX 980 in this document. With 2048 CUDA Cores and 4GB of GDDR5 memory, GM204 is the fastest GPU in the world, yet with a TDP of just 165W, it's also the most efficient.

# **GM204 Hardware Architecture In-Depth**

Figure 2: GM204 Full-chip block diagram

Like Fermi and Kepler, GM204 is composed of an array of Graphics Processing Clusters (GPCs), Streaming Multiprocessors (SMs), and memory controllers. GM204 consists of four GPCs, 16 Maxwell SMs (SMM), and four memory controllers. GeForce GTX 980 uses the full complement of these architectural components (if you are not well versed in these structures, we suggest you first read the <u>Kepler</u> and <u>Fermi</u> whitepapers).

Another version of the chip, with 13 SMs, will ship concurrently and be called GeForce GTX 970. In the future we plan to offer additional products based on GM204 that will ship with different combinations of GPCs, SMs, and memory controllers to address various segments of the graphics market.

In GeForce GTX 980, each GPC ships with a dedicated raster engine and four SMMs. Each SMM has 128 CUDA cores, a PolyMorph Engine, and eight texture units. With 16 SMMs, the GeForce GTX 980 ships with a total of 2048 CUDA cores and 128 texture units.

The GeForce GTX 980 features four 64-bit memory controllers (256-bit total). Tied to each memory controller are 16 ROP units and 512KB of L2 cache. The full chip ships with a total of 64 ROPs and 2048KB of L2 cache (this compared to 32 ROPs and 512K L2 on GK104).

The following table provides a high-level comparison of Maxwell vs. our previous-generation GK104 GPU:

| GPU                   | GeForce GTX 680 (Kepler) | GeForce GTX 980 (Maxwell) |

|-----------------------|--------------------------|---------------------------|

| SMs                   | 8                        | 16                        |

| CUDA Cores            | 1536                     | 2048                      |

| Base Clock            | 1006 MHz                 | 1126 MHz                  |

| GPU Boost Clock       | 1058 MHz                 | 1216 MHz                  |

| GFLOPs                | 3090                     | 4612 <sup>1</sup>         |

| Texture Units         | 128                      | 128                       |

| Texel fill-rate       | 128.8 Gigatexels/sec     | 144.1 Gigatexels/sec      |

| Memory Clock          | 6000 MHz                 | 7000 MHz                  |

| Memory Bandwidth      | 192 GB/sec               | 224 GB/sec                |

| ROPs                  | 32                       | 64                        |

| L2 Cache Size         | 512KB                    | 2048KB                    |

| TDP                   | 195 Watts                | 165 Watts                 |

| Transistors           | 3.54 billion             | 5.2 billion               |

| Die Size              | 294 mm²                  | 398 mm²                   |

| Manufacturing Process | 28-nm                    | 28-nm                     |

The GeForce GTX 980 has double the SMs compared to the GK104 GPU used in the GeForce GTX 680 released two years ago. Because of the changes implemented in GTX 980's new Maxwell SM, we were able to integrate 2x more SMs without doubling the die size. With each SM also containing its own dedicated PolyMorph Engine, GeForce GTX 980 also has twice the number of geometry units as its direct predecessor. We'll be discussing more details on the new SM design in the next section of the whitepaper.

Based on efficiency and workload analysis, and math vs. texture processing requirements of modern games, NVIDIA engineers determined that eight texture units per SMM is the best architectural balance for Maxwell; therefore, the total number of texture units is the same as Kepler, 128. However, thanks to GeForce GTX 980's higher clocks, texture fill rate improves by 12% from one generation to the next. To improve performance in high AA/high resolution gaming scenarios, we doubled the number of ROPs

<sup>&</sup>lt;sup>1</sup> The GFLOPS and texel fill rates in this chart are based on GPU Base Clock

from 32 to 64. Again, thanks to the added benefit of higher clocks, pixel fill-rate is actually more than double that of GTX 680: 72 Gpixels/sec for GTX 980 versus 32.2 Gpixels/sec for GTX 680.

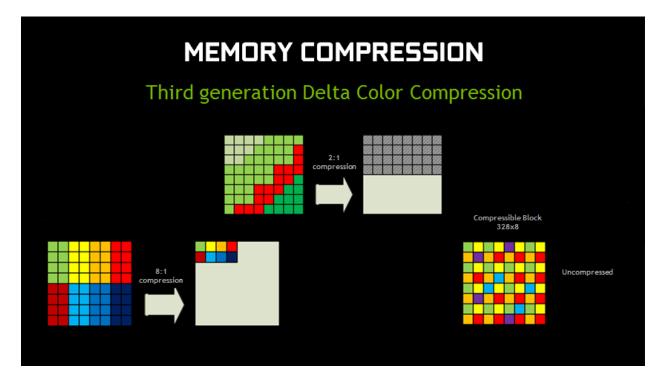

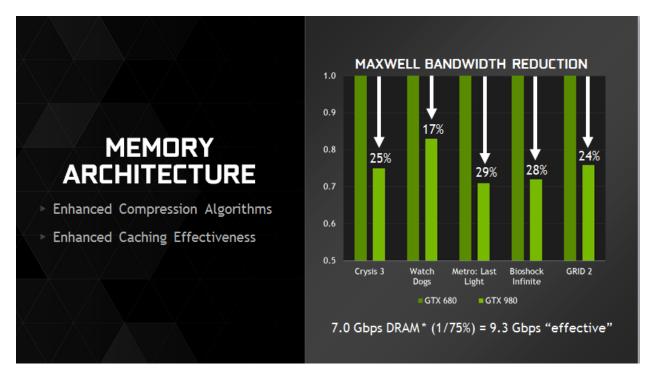

The memory subsystem has also been significantly revamped. GTX 980's memory clock is over 15% higher than GTX 680, and GM204's cache is larger and more efficient than Kepler's design, reducing the number of memory requests that have to be made to DRAM. Improvements in our implementation of memory compression provide a further benefit in reducing DRAM traffic—effectively amplifying the raw DRAM bandwidth in the system.

| SMM                                          |                                                                              |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|----------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------|

|                                              | PolyMorph Engine 3.0 Vertex Fetch Tessellator Viewport Transform             |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              |                                                                              |                                                                               | Attrib                                                       | ute Setup                                                                         |                                                             | ]       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Stream O                                                                     |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Instruction Cache                                                            |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Instruction Buffer Instruction Buffer                                        |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Warp Scheduler                                                               |                                                                               |                                                              |                                                                                   |                                                             |         | Warp Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

| Di                                           | ispatch Uni                                                                  | it                                                                            |                                                              | Dispatch Ur                                                                       |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Register File (16,384 x 32-bit) Register File (16,384 x 32                   |                                                                               |                                                              |                                                                                   |                                                             | 32-bit) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

| Core                                         | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                             | SFU                                                         |         | Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                                                                         | Core                                                                          | Core                                                         | LD/ST                                                                              | SFU                                    |

|                                              | Texture / L1 Cache                                                           |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Tex Tex Tex                                                                  |                                                                               |                                                              |                                                                                   |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               |                                                              |                                                                                    |                                        |

|                                              | Tex                                                                          |                                                                               |                                                              | Tex                                                                               | Texture                                                     |         | I Gacile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Tex                                                                          |                                                                               |                                                              | Tex                                                                                |                                        |

|                                              |                                                                              | nstructi                                                                      |                                                              |                                                                                   | Texture                                                     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |                                                                               | on Buffe                                                     |                                                                                    |                                        |

|                                              | 1                                                                            | Warp So                                                                       | cheduler                                                     | ər                                                                                |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                            | Warp So                                                                       | cheduler                                                     | ər                                                                                 | nit                                    |

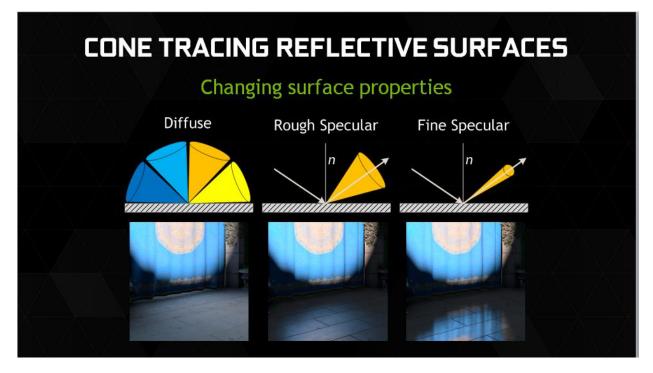

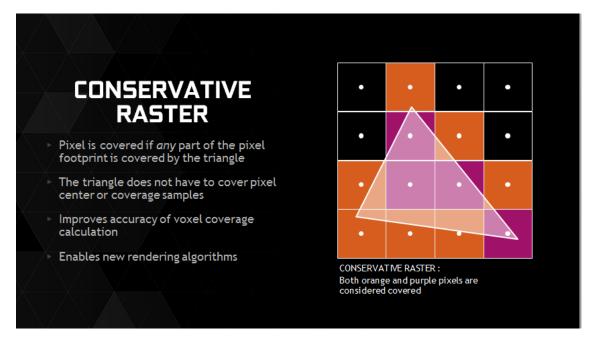

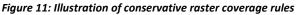

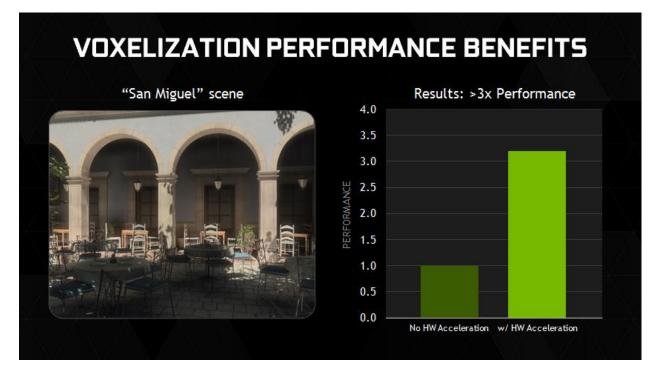

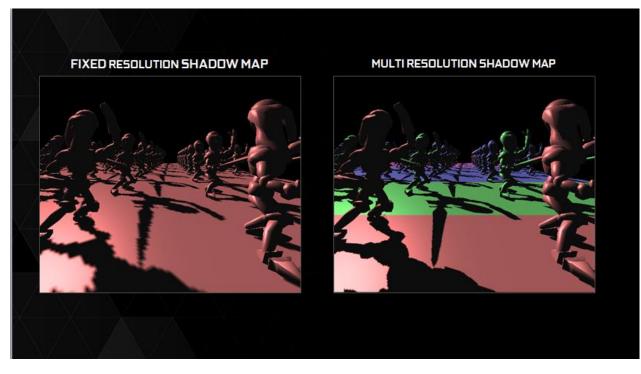

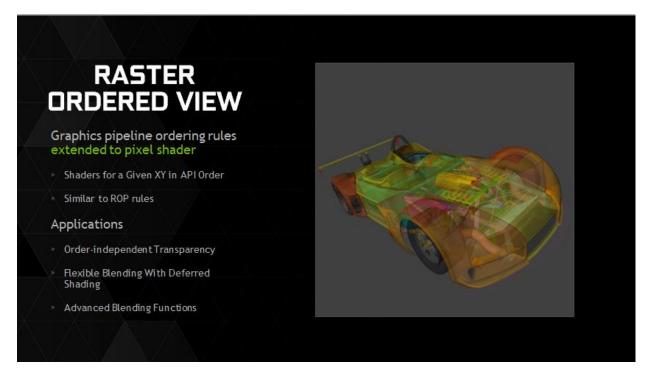

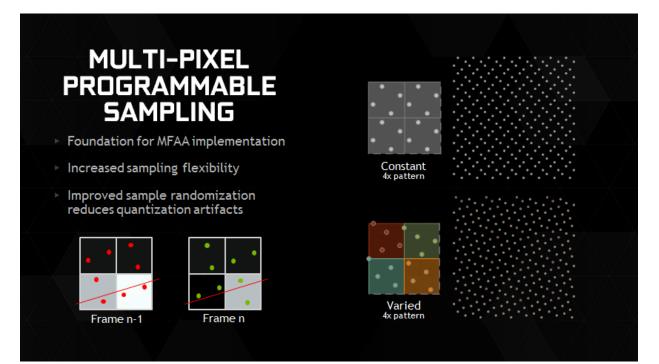

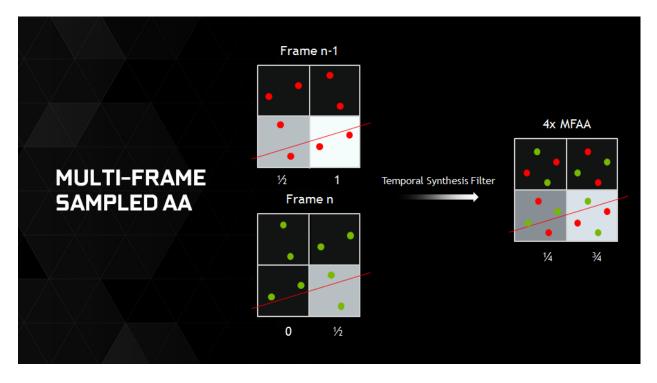

|                                              | ispatch Un                                                                   | Warp Se                                                                       | cheduler<br>[                                                | ər<br>Dispatch U                                                                  |                                                             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ispatch Un<br>♥                                                              | Warp So<br>it                                                                 | cheduler<br>[                                                | er<br>Dispatch Ur                                                                  | nit                                    |